干货 | 高深宽比刻蚀和纳米级图形化技术 推动存储器发展的关键技术路线图

在半导体存储器技术持续发展的道路上,高深宽比刻蚀和纳米级图形化已成为推动存储器密度和性能提升的两大核心技术。随着存储器从2D NAND向3D NAND的演进,以及DRAM技术的不断微缩,这些先进工艺对实现更高存储容量和更低功耗至关重要。

一、高深宽比刻蚀技术的突破与进展

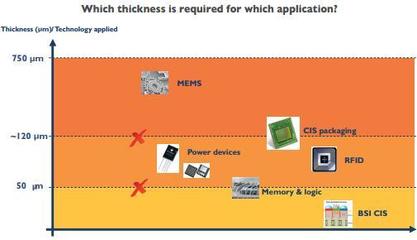

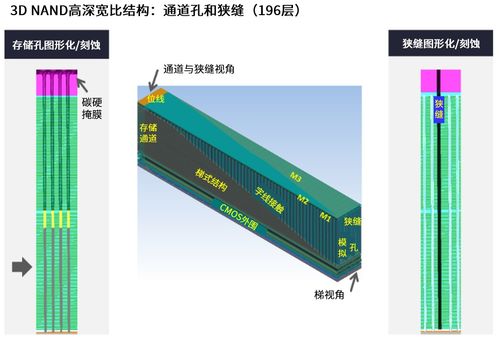

高深宽比刻蚀是指在硅基或其他材料上刻蚀出深度远大于宽度的结构。在3D NAND存储器中,这一技术用于制造垂直堆叠的存储单元,允许在有限的芯片面积内容纳更多存储层。随着堆叠层数从64层向200层以上迈进,高深宽比刻蚀的挑战日益增加:

- 刻蚀均匀性:确保每一层的刻蚀深度和形貌一致。

- 选择比控制:避免对掩模和底层材料的过度刻蚀。

- 侧壁粗糙度:减少缺陷,提高存储器可靠性。

近年来,原子层刻蚀和等离子体工艺优化显著提升了高深宽比刻蚀的精度,为下一代存储器的量产奠定了基础。

二、纳米级图形化技术的创新路径

纳米级图形化通过极紫外光刻和多层自对准技术,实现了特征尺寸的持续缩小。在存储器中,这直接关系到单元密度和存取速度:

- EUV光刻应用:使DRAM和NAND的特征尺寸降至10纳米以下,减少了多重曝光步骤,提升了生产效率。

- 自对准多重图案化:通过化学和沉积工艺,在无需额外光刻的情况下生成更精细的图形,适用于高密度存储器阵列。

- 新材料集成:结合二维材料或相变材料,纳米级图形化助力新兴存储器如RRAM和MRAM的实现。

三、存储器技术路线图:从当前到未来

基于高深宽比刻蚀和纳米级图形化的进步,存储器技术路线图可概括为:

- 短期(2023-2025年):3D NAND堆叠层数超过500层,DRAM单元尺寸缩至10纳米以下,依赖EUV和先进刻蚀工艺。

- 中期(2026-2030年):引入混合键合和晶圆级集成,结合高深宽比结构实现Terabit级存储器;纳米级图形化推动神经形态存储和存算一体应用。

- 长期(2030年后):探索原子级刻蚀和量子图形化,可能颠覆传统存储器架构,实现超高密度和低能耗存储。

四、挑战与展望

尽管技术进步显著,但高深宽比刻蚀面临材料应力控制问题,而纳米级图形化则需克服光刻成本和缺陷率上升的瓶颈。未来,跨学科合作与AI辅助工艺优化将成为关键。总体而言,这些技术将持续驱动存储器行业向更高性能、更大容量迈进,为人工智能、物联网和大数据应用提供核心支撑。

高深宽比刻蚀和纳米级图形化不仅是存储器微缩的基石,更是未来存储技术创新的引擎。通过持续研发和产业链协同,我们有望在不久的见证存储器技术的又一次飞跃。

如若转载,请注明出处:http://www.szbosun.com/product/535.html

更新时间:2025-10-20 17:33:28